发布日期:2026-04-24

Against the backdrop of rapid AI advancement and accelerated iteration of infrastructure, the compute demand for supernode has surged on a massive scale. As the foundational core for AI large-model training and high-performance computing (HPC), high-speed interconnect technology has emerged as a key battleground for corporate competition. The UALink™ (Ultra Accelerator Link™) specification—featuring a fully open ecosystem with ultra-high bandwidth, ultra-low latency, and native memory semantics—has become a pivotal interconnect technology for the next-generation supernode.

Netforward is actively advancing the UALink ecosystem development and technology evolution. The company has successfully completed the full-cycle IC design of dedicated UALink IP and switch, alongside comprehensive prototype verification on FPGA platforms and protocol conformance testing. This milestone significantly accelerates the implementation of the UALink specification within AI infrastructure.

Netforward 's UALink IP and switch implement the UALink 1.0 specification,and will support more advanced features in the UALink 2.0 release such as Link Resiliency and Link Folding. These products deliver key technical advantages including high bandwidth, low latency, and high reliability, enabling full-mesh interconnection of up to 100+ AI accelerators within a supernode. By integrating in-network computing, comprehensive RAS (Reliability, Availability, Serviceability) capabilities, they provide an efficient, open, and highly compatible foundation for scale-up network in AI large-model training and HPC scenarios.

Prototype Verification on FPGA Platforms

The verification covers two typical scenarios: Direct Connection and Switched Networking.

1. Direct Connection Scenario

Two FPGA-VU19P systems are interconnected via DAC cables to simulate point-to-point GPU communication utilizing the UALink interface IP. This setup validates the protocol functionalities of the Physical Layer (PL), Data Link Layer (DL), Transaction Layer (TL), and UALink Protocol Layer Interface (UPLI).

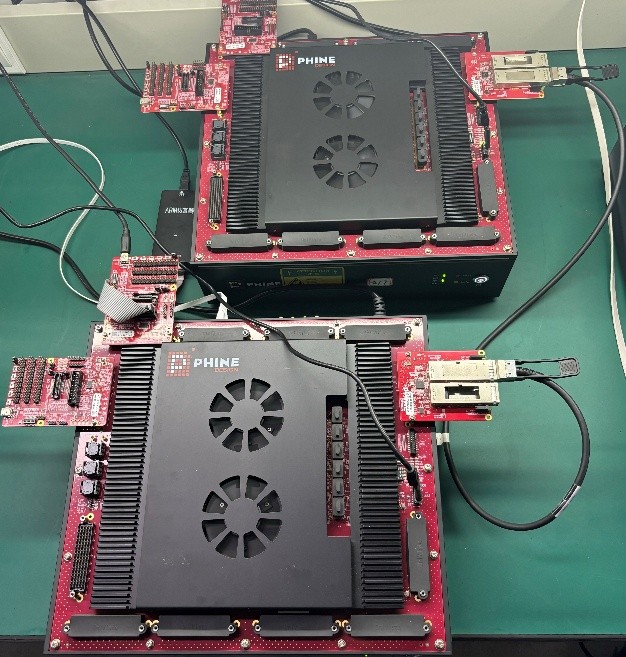

Figure 1. UALink Interface IP Prototype Verification Platform

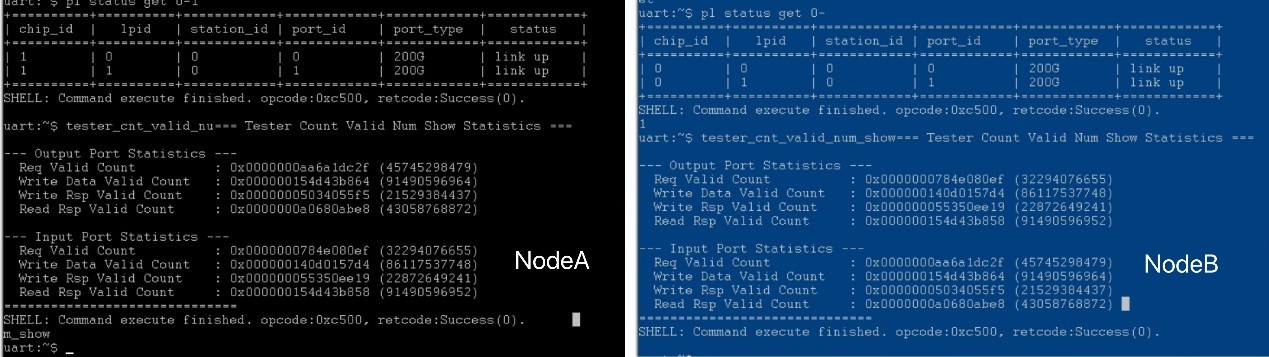

The test utilizes the private packet generator to simulate mixed requests from GPUs. The UALink interface IP undergoes continuous transmission and reception tests in both X2 and X4 modes. Results confirm that the UALink interface IP on both sides successfully encapsulates, parses, transmits, and receives service data as designed, with interface statistics remaining accurate and valid throughout the test.

Figure 2. Test Results of the UALink Interface IP Prototype Verification Platform

2. Switched Networking Scenario

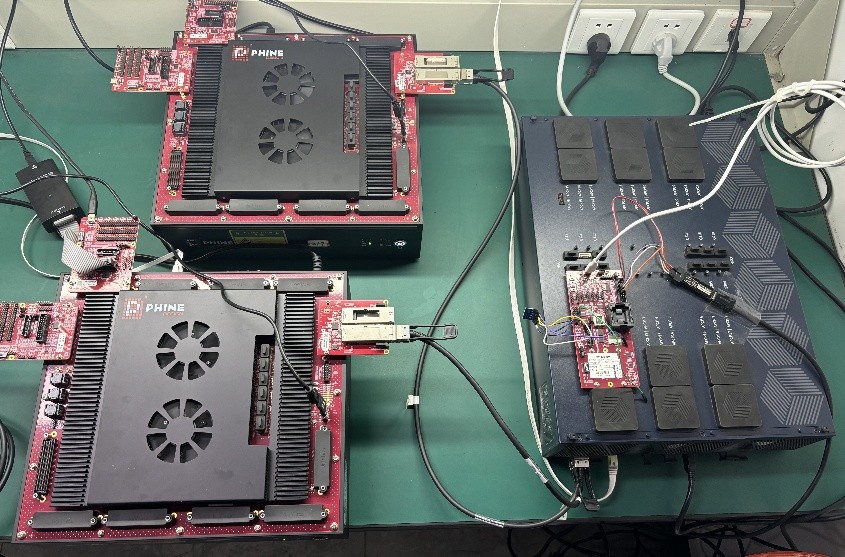

This scenario primarily verifies the switch's interconnect capability in a typical scale-up network. Two FPGA-VU19P systems simulate GPUs, while one FPGA-VP1902 system serves as the UALink switch. The three systems are interconnected via DAC cables to form a switched network. The test scope encompasses full protocol functionality validation of the UALink switch, RAS mechanisms, PCIe interface, and SoC features.

Figure 3. UALink Switch Prototype Verification Platform Environment

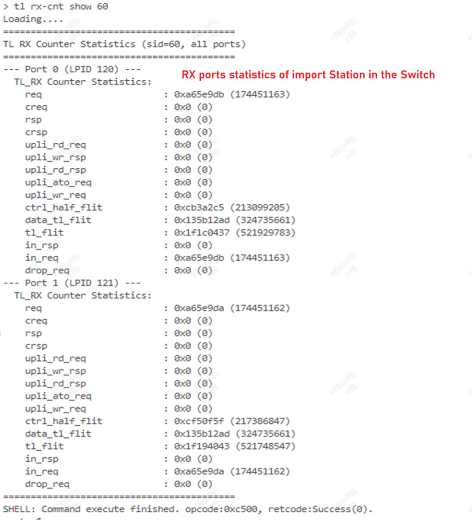

The test utilizes the packet generator to simulate write/writefull/read/AtomicR/AtomicNR requests and corresponding responses from GPUs, with continuous verification spanning over 24 hours. Results indicate that the UALink switch system correctly receives, parses, and forwards data in accordance with design specifications, exhibiting stable system operation and accurate, valid statistical data.

Figure 4. Test Results of the UALink Switch Prototype Verification Platform

Additionally, Netforward has conducted comprehensive functional, performance, and in-network computing specification tests on the UALink interface IP and switch system via hardware emulation platforms. Test results demonstrate that the products meet the efficient and reliable transmission requirements of interconnect scenarios in AI and HPC. Key performance metrics, including latency, bandwidth, and link bandwidth utilization, have achieved expected design targets, showcasing outstanding overall performance.

The completion of full-cycle design and end-to-end prototype verification for the UALink IP and switch provides critical chip-level support for the UALink specification to transition from standard specification to engineering implementation. This work has thoroughly validated the protocol's functionality, performance, and networking feasibility, thereby accelerating the industrialization of the UALink open ecosystem. It establishes a solid foundation for the mass production and large-scale deployment of interconnect chips in next-generation AI supernode, while fostering an open and compatible ecosystem for high-end interconnect technologies.